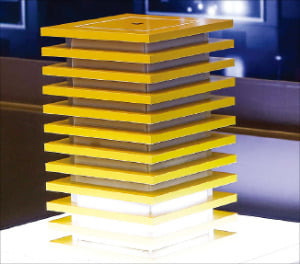

“D램이 단층 건물이라면 HBM은 여러 층의 메모리를 쌓아 올린 아파트입니다. 설계 단계에서부터 엔비디아의 그래픽처리장치(GPU)에 최적화된 HBM을 개발하는 데 집중하고 있습니다.”

고대역폭메모리(HBM)의 세계적 권위자인 김정호 KAIST 전기및전자공학부 교수(사진)가 11일 ‘차세대 HBM 로드맵 기술 발표회’를 열고 이렇게 밝혔다. 김 교수는 이날 SK하이닉스가 상용화를 앞둔 6세대 HBM인 ‘HBM4’부터 2040년까지 이어질 HBM의 진화 과정을 소개했다.

◇ 고객 맞춤형으로 진화하는 HBM

HBM은 여러 층의 메모리를 수직으로 쌓아 층간을 입출력(IO) 단자로 연결해 만든다. 수직 적층된 D램 칩 사이를 관통하며 데이터를 이동시키는 통로 구실을 하는 실리콘관통전극(TSV) 설계가 중요하다. TSV는 IO의 길을 인도하는 역할도 한다.

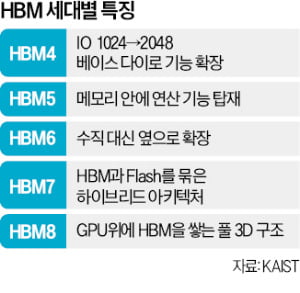

상용화된 최신 제품인 HBM3E의 IO는 1024개지만 내년 출시될 예정인 HBM4는 두 배인 2048개다. HBM5는 4096개, HBM6는 8192개에 달한다. 2040년께 개발될 HBM8은 IO가 1만6384개까지 확장될 것으로 예측됐다. 정보가 오가는 ‘데이터 고속도로’가 그만큼 넓어진다는 뜻이다.

‘HBM 커스터마이징’ 시대가 처음 열릴 것이란 전망도 나왔다. 김 교수는 “HBM4부터는 ‘커스텀 베이스 다이’ 개념이 도입돼 고객사가 원하는 기능을 바닥층부터 직접 설계해 반영할 수 있다”며 “엔비디아 같은 팹리스가 메모리 내부에 연산 코어와 메모리 컨트롤러 등을 설계 단계부터 반영할 수 있을 것”이라고 예상했다. HBM5에서는 메모리와 연산 기능의 결합이 본격화된다. ‘컴퓨팅 다이’가 메모리 내부에 들어가 데이터 이동 거리를 최소화하고 연산 효율을 높이는 설계가 도입된다. 발열을 줄이기 위해 ‘액침 냉각’ 기술도 HBM5부터 적용된다. 김 교수는 “액침 냉각은 반도체를 특수 냉각 액체에 담가 열을 식히는 방식으로, 고층 건물 전체에 냉방 시스템을 설치한 것에 비유할 수 있다”고 밝혔다.

HBM6는 새로운 공간 효율화 전략이 적용된다. 더 높이 쌓는 대신 옆으로 확장하는 ‘멀티 타워’ 구조가 등장한다. 건물 옆에 또 다른 건물을 붙이고 그 사이를 빠른 통로로 연결해 데이터를 주고받는 방식이다. 데이터가 흐르는 경로인 인터포저(기판과 칩을 연결하는 중간 매개체)의 역할도 기존 방식에서 벗어나 능동적으로 전기를 관리하고 연산까지 수행하는 ‘스마트 인터포저’로 진화한다.

◇ 고대역폭 플래시 메모리(HBF) 온다

HBM7에서는 완전히 새로운 개념이 도입된다. 기존 D램 중심에서 벗어나 낸드플래시를 함께 적층한 고대역폭 플래시 메모리(HBF) 개념이 HBM7에서 등장할 것으로 예상된다. 김 교수는 “HBM의 속도, 플래시 용량, LPDDR(최신 저전력 D램)의 전력 효율을 결합해 상황에 따라 메모리 자원을 유연하게 활용하는 ‘하이브리드 메모리’ 구조가 실현될 것”이라고 설명했다. 메모리 안에 장단기 기억과 연산 기능이 내장된 일종의 ‘통합 지능 플랫폼’이 자리 잡는 셈이다. 내부 냉각 기술은 적층된 칩 사이에 직접 냉각수를 흘려 보내는 ‘임베디드 쿨링’으로 발전할 전망이다.

HBM8는 단순한 적층을 넘어 완전한 3D 공간 구조를 구현한다. 메모리와 GPU가 한 몸처럼 통합돼 인터포저 위뿐 아니라 양면에까지 입체 패키징이 가능해진다. IO는 1만6384개로 HBM 성능이 정점에 도달하는 시점이다. 김 교수는 “AI 시대 메모리는 단순한 저장 장치가 아니라 시스템 반도체로 발전할 것”이라고 강조했다. 메모리가 단순히 보관만 하는 ‘서랍장’이 아니라 데이터를 분류하고 정리도 하는 똑똑한 서랍장으로 진화랄 것이란 설명이다.

강경주 기자 qurasoha@hankyung.com

6 days ago

7

6 days ago

7

!["일단 살아남자"…외국산 엔진에 종속되는 'K게임 생태계' [긱스]](https://img.hankyung.com/photo/202506/AA.40848005.1.jpg)

![전병곤 "원하는 AI 모델만 고르면 됩니다 최적화·배포·운영 대신해 드려요" [긱스]](https://img.hankyung.com/photo/202506/AA.40848006.1.jpg)

![천하람 “국민의힘, 죽어버린 나무…물 줄 필요 있나” [정치를 부탁해]](https://dimg.donga.com/wps/NEWS/IMAGE/2025/06/02/131732216.1.jpg)

![조승래 “지귀연 판사 제보 여러건…법원-공수처가 확인해야” [정치를 부탁해]](https://dimg.donga.com/wps/NEWS/IMAGE/2025/05/19/131636504.1.jpg)

![[포토] 투표용지 인쇄 시작](https://img.hankyung.com/photo/202505/AA.40611422.1.jpg)

English (US) ·

English (US) ·